## Analytical XTEM Study of Ir/InAlAs Interfacial Reaction for InP-based High Electron Mobility Transistors (HEMTs) Gate Technology

Liang Wang, 1,2 Weifeng Zhao, 1,3 and Ilesanmi Adesida 1,2,3

1. Micro and Nanotechnology Lab, 2. Dept Materials Science and Engineering, and 3. Dept Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL 61801

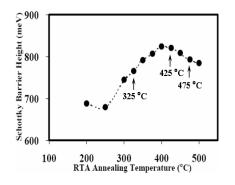

Schottky contact property is one of the essential concerns for the application of InP-based HEMTs where high Schottky barrier height  $(\varphi_B)$  is desirable for the reduction of gate leakage current and tailoring of threshold voltage. Thermal annealing is used to activate the metallization and to obtain high  $\varphi_B$ . For example, the conventional Pt gate has a  $\varphi_B$  of 700 meV when deposited on InAlAs. While upon annealing at 200 °C,  $\varphi_B$  increases to 800 meV [1]. Further annealing causes performance degradation. The low annealing temperature  $(T_a)$  of Pt gate makes the reliable performance of devices a big concern. XTEM study demonstrated that prolonged thermal storage of Pt contacts resulted in extensive in-diffusion of Pt into the semiconductor [2] and a failure of the device could thus occur. Alternatively, an Ir-based metallization scheme with comparable  $\varphi_B$  to Pt but higher  $T_a$  has been developed by our group [1].  $\varphi_B$  as a function of  $T_a$  for the Ir-based gate to InAlAs/InGaAs HEMT layers is plotted in Fig. 1. Below the optimal condition  $(T_a=400\ ^{\circ}C)$ ,  $\varphi_B$  increases monotonically. Beyond this temperature, an over annealing occurs and  $\varphi_B$  drops gradually. In present study, a TEM investigation is carried out on samples with different  $T_a$ , namely, 325 °C, 425 °C and 475 °C which correspond to under-annealing, optimal annealing and over-annealing, respectively, to elucidate the Schottky barrier formation mechanism and the over-annealing mechanism.

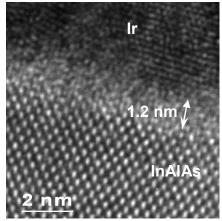

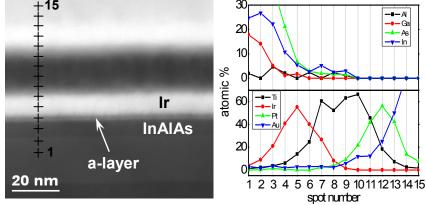

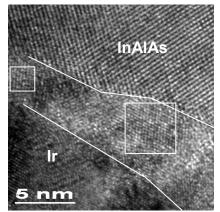

The epilayer structure and  $\varphi_B$  measurement procedure could be found elsewhere [2]. The e-beam deposited gate contacts consisted of Ir (10 nm)/Ti (20 nm)/Pt (10 nm)/Au (160 nm) which was then annealed for 30 s under N<sub>2</sub> ambient. XTEM samples were prepared by sample gluing, grinding and ion milling. TEM works were done on a JEOL 2010F TEM for microstructure and microchemistry characterization. The layered structure of the as deposited contacts is clearly revealed by Z-contrast image in Fig. 2a. The Ir layer has polycrystalline morphology from the HRTEM image in Fig. 2b. No interfacial reaction between Ir and InAlAs could be resolved and Ir is in intimate contact with InAlAs. When annealed at 325 °C (Fig. 3), Ir diffuses into InAlAs and forms an interfacial amorphous layer (a-layer) with a depth of ~1.2 nm. The formation of a-layer has been observed in several systems such as metal/Si [3] and Pt/InAlAs [2]. We believe that the formation of the a-layer and its composition is essential for Schottky barrier formation. The a-layer is too thin to confidently obtain the composition by EDS though. Further annealing to the optimal condition yields an even thicker a-layer (2.5 nm) as shown in Fig. 4a. EDS composition profiles across the metallization is drawn in Fig. 4b. The Ir layer is thick enough to block Ti in-diffusion; out-diffusion of As and In from the epilayer is manifested suggesting the a-layer consists these two elements. Annealing at 475 °C creates significant different interfacial structure and that the a-layer starts to crystallize (Fig. 5). This crystallized layer has a thickness of ~4 nm which means a significant portion (50%) of the InAlAs layer is consumed. EDS analysis indicates these crystals have an average composition of ~34 % Ir (at. % here and after), ~48 % As and 18% In. An investigation of Ir-Al-As and Ir-In-As ternary phase diagrams indicates that IrAs<sub>2</sub>, IrAl or IrIn<sub>2</sub> could be the crystal phases. The results suggest that the a-layer is the  $\varphi_B$  formation mechanism in Ir/InAlAs. The formation of stable crystalline phases or the consumption of the InAlAs layer may degrade contact performance.

## References

- [1] S. Kim et al., Electron. Lett., 41 (2005) 665.

- [2] S. Kim et al., Appl. Phys. Lett., 87 (2005) 232102.

- [3] L.J. Chen et al, Mater. Sci. Eng. R29 (2000) 115.

- [4] This work was supported by NSF ANI (01-21662 ITR) and ONR (N00014-01-1000). TEM works were carried out at the Center for Microanalysis of Materials at the University of Illinois (DOEFG02-91-Er45439). Assistance of J.G. Wen and C.H. Lei on the TEM is acknowledged.

Au

0.22 nm lr (111)

Pt

Ti

Ir

InAlAs

FinGaAs

InP

FIG. 1.  $\varphi_B$  as a function of  $T_a$  for Ir gate metallization on InAlAs/InGaAs

FIG. 2. As deposited structure. (a) Z-contrast image, (b) HRTEM image of the Ir/InAlAs layers.

FIG. 3. HRTEM image of after annealed at 325 °C

FIG. 4. (a) Z-contrast image after annealed at 425 °C. (b) EDS composition profiles.

FIG. 5. HRTEM image of after annealed at 475 °C